### Cybersecurity Research Acceleration Workshop and Showcase

October 11, 2017 | Indianapolis, IN

## **Quad Chart for:**

# Zero-power Dynamic Signature for Trust Verification of Passive Sensors and Tags

#### **Challenge:**

Robust and secure authentication of passive Internet-of-things at minimal computational cost and complexity.

#### **Solution:**

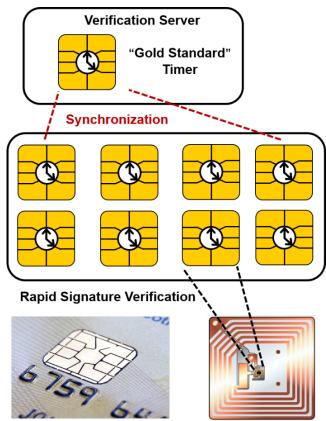

- Self-powered chip-scale clock that operate without any external powering.

- The clocks are synchronized with respect to each other without any communications.

- Trust verification and authentication based on the degree of synchronization of an array of clocks.

- Tampering or change in supply-chain conditions desynchronizes the clocks and can be detected.

(GRANT INFO) NSF STARSS: 1525476 SRC Contract:2015-TS-2640

PI: Shantanu Chakrabartty

#### **Value proposition:**

- Dynamic Authentication: Technology more secure than existing static techniques and is immune to different attack models.

- Zero-power and minimal computational foot-print:

Technology does not require any external powering and can be used for authenticating any passive assets.

Chip-scale solution: Micro-scale device can be integrated with existing wireless solutions.

#### What we need to TTP

- Full chip integration

- Software interface development

#### **Contact us**

- Shantanu Chakrabartty

- Washington University in St. Louis, Email: <a href="mailto:shantanu@wustl.edu">shantanu@wustl.edu</a>